paul_met

Established Member

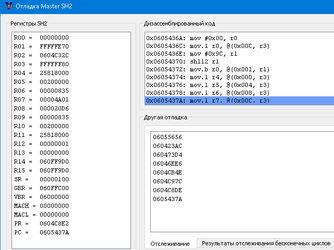

Digging into the resources of a particular game, I often come across the following code (see screenshot). I understand that this is reading / writing using DMA. But I don't fully understand how it works. From what I figured it out:

A couple more questions arise:

- The value in register R4 is the address of data reading (in the this case, reading from CD, but it is not clear from which sector).

- The value in register R5 is the address for writing data (everything is clear with this).

- The value in register R6 is the size of the data block that will be read and written (using 32 bits value, so the data size is divisible by 4).

- The value in register R7 is some kind of bus usage identifier (I didn't find any explanation for this in the documentation). There are different types of identifier (5A01, 5E01 and so on).

- The value in register R3 is a buffer address or what? (I also did not find anything like this in the documentation).

A couple more questions arise:

- In what cases can and should you use DMA transfer?

- Will the read / write speed differ when using DMA transfer as compared to the standard MOV instruction?