mrkotfw

Mid Boss

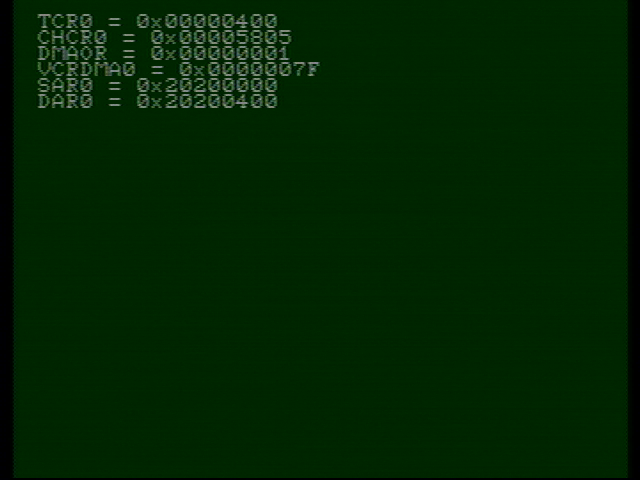

I'm looking to have the SuperH generate an interrupt for when a transfer in the DMAC is complete. I enabled interrupts (bit 2 in CHCR0 and CHCR1). I also set the vector number (ranges from 0-127) in register VCRDMA0 and VCRDMA1.

I then set the vector, say 127 to the interrupt handling routine. That amounts to writing to address VBR + (127 << 2) where VBR is 0x06000000.

For the life of me, I can't get INTC to generate the interrupt.

Is there anything special about these on-chip interrupts? Why does it range from 0-127? Wouldn't it conflict with other predefined interrupts?

I then set the vector, say 127 to the interrupt handling routine. That amounts to writing to address VBR + (127 << 2) where VBR is 0x06000000.

For the life of me, I can't get INTC to generate the interrupt.

Is there anything special about these on-chip interrupts? Why does it range from 0-127? Wouldn't it conflict with other predefined interrupts?