I found an interesting thing about the A-Bus CS2. The bios uses different addresses to read 16 and 32 bits data from the CD block: 0x25898000 and 0x25818000 respectively. The bios reads File Info and TOC data in words from 0x25898000, and sector data in long words from 0x25818000. When address bit 19 is 0 SCU does two consecutive reads from the A-Bus. Only address bits AA[5:2] and AA[14:12] are connected to YGR.

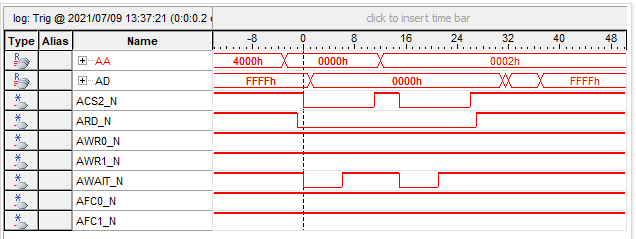

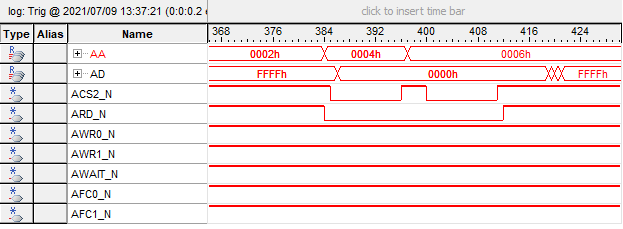

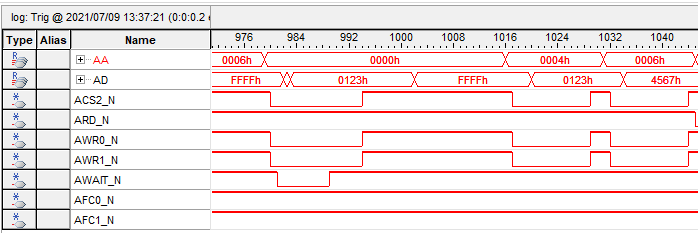

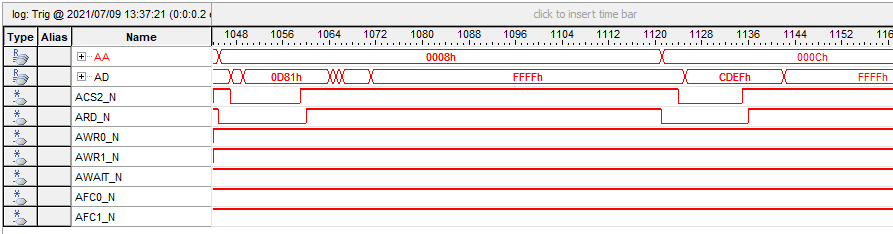

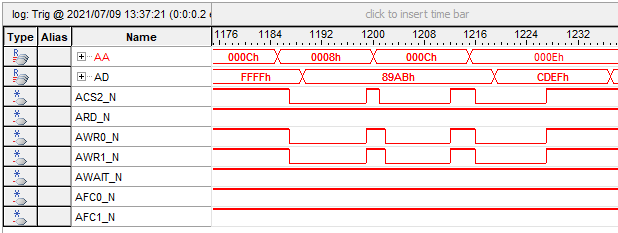

I wrote a simple test program and captured A-Bus logs:

0x25818000 read word:

0x25818004 read long:

0x25818000 write word,0x25818004 write long:

0x25898008 read word,0x2589800C read long:

0x25898008 write word,0x2589800C write long:

I couldn't find any notes about it in SCU manuals.

I wrote a simple test program and captured A-Bus logs:

Code:

temp16 += *(volatile uint16_t *)(0x25818000);

temp32 += *(volatile uint32_t *)(0x25818004);

*(volatile uint16_t *)(0x25818000) = 0x0123;

*(volatile uint32_t *)(0x25818004) = 0x01234567;

temp16 += *(volatile uint16_t *)(0x25898008);

temp32 += *(volatile uint32_t *)(0x2589800C);

*(volatile uint16_t *)(0x25898008) = 0x89AB;

*(volatile uint32_t *)(0x2589800C) = 0x89ABCDEF;0x25818000 read word:

0x25818004 read long:

0x25818000 write word,0x25818004 write long:

0x25898008 read word,0x2589800C read long:

0x25898008 write word,0x2589800C write long:

I couldn't find any notes about it in SCU manuals.